日益发展的技术对芯片电压测试的挑战

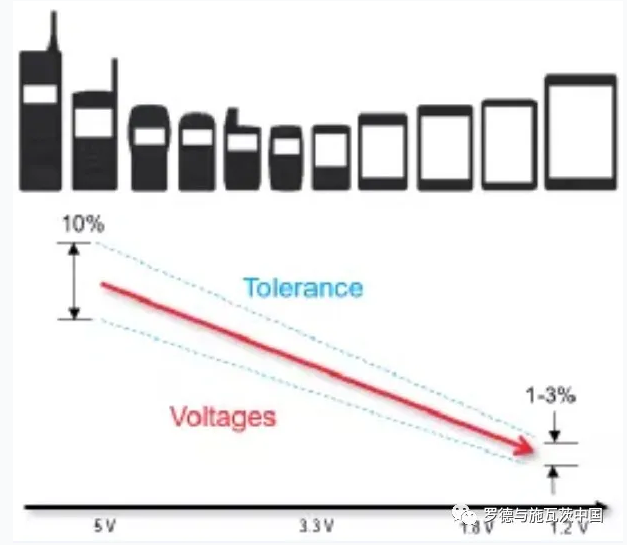

随着5G、车联网等技术的飞速发展,信号的传输速度越来越快,集成电路芯片的供电电压随之越来越小。早期芯片的供电通常是5V和3.3V,而现在高速IC的供电电压已经到了2.5V、1.8V或1.5V,有的芯片的核电压甚至到了1V。芯片的供电电压越小,电压波动的容忍度也变得越苛刻。对于这类供电电压较小的高速芯片的电压测试用电源噪声表示,测求要求从±5%到 ±-1.5%,乃至更低。

如果芯片的电源噪声没有达到规范要求,就会影响产品的性能,乃至整机可靠性。因此工程师需要准确地测量现代电路产品中的芯片电压的电源噪声。

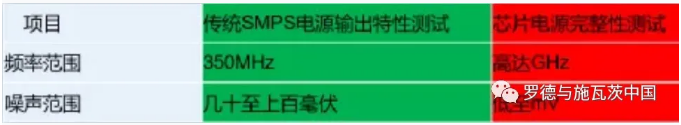

芯片电源噪声的特点

更小幅度,更高频率

以往电源噪声的要求维持在几十mV的量级,而随着芯片电压的降低,很多芯片的电源噪声已经到了mV的量级,某些电源敏感的芯片要求甚至到了百uV的量级。直流电源上的噪声是数字系统中时钟和数据抖动的主要来源。处理器、内存等芯片对直流电源的动态负载随着各自时钟频率而发生,并可能在直流电源上耦合高速瞬态变化和噪声,它们包含了1 GHz以上的频率成分。

因此与传统的电源相比,芯片电源的噪声具有频率高/幅度小等特点,这就为了工程师准确地测得芯片的电源噪声带来了挑战。

表1:传统电源和芯片电源频率和噪声范围

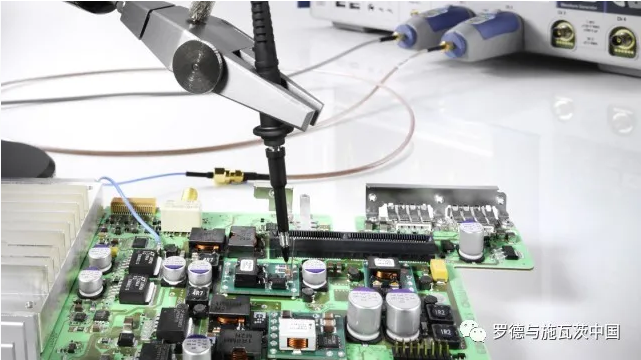

电源分布网络(PDN)引入的噪声干扰

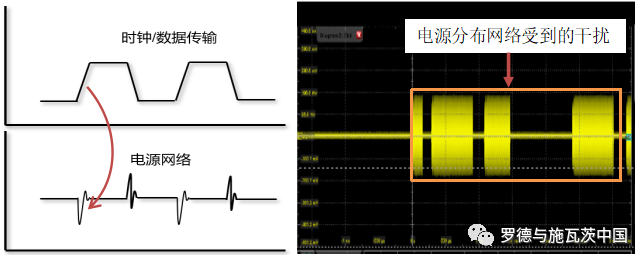

为了保证电路上各个芯片的供电,电源分布网络(PDN)遍布整个PCB。如果电源分布网络靠近时钟或者数据的PCB走线,那么时钟/数据的变化会耦合到电源分布网络上,也会成为电源噪声的来源。在这种情况下,工程师还需要定位电源噪声的来源,以便后续调整PCB的布局和布线,减少PDN网络受到的干扰。

图2:时钟,数据传输线耦合到电源分布网络的干扰

影响电源噪声测试准确性的因素

示波器是电源噪声测试的重要仪器。为了能够准确地测量GHz带宽内mV级别的电源噪声,并定位干扰电源分布网络的噪声来源,需要考虑如下因素:示波器的底噪,探头的衰减比,示波器的偏置补偿能力,探头的探接方式,以及示波器的FFT能力等等。

示波器底噪

图3:示波器底噪对电源噪声测试结果的影响

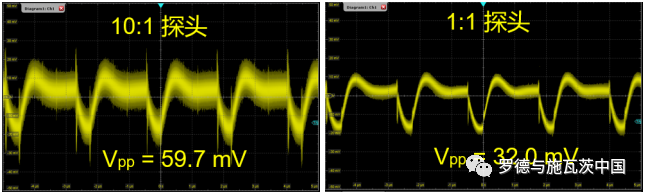

探头的衰减比

目前最常用的500MHz带宽的无源探头的衰减比为10:1,其会放大示波器的底噪,影响电源噪声测试的不确定性。

如果用传统的衰减比为1:1的无源探头,可以避免放大示波器的底噪。但是这种探头的带宽一般在38MHz,无法测到更高频率的电源噪声。同样会影响电源噪声测试的不确定性。

所以,为了准确测量电源噪声,需要一款衰减比为1:1,带宽到GHz的探头。

图4:头的衰减比对电源噪声测试的影响

示波器的偏置补偿能力