问题解决思路:找到问题来源点,解决方法就多种多样了。在此笔者推荐三种方法一起用:1. 对PCIE_PERST_N复位信号加滤波;2. 做好整机/模块的ESD保护;3. FPGA对PCIE_PERST_N信号做判断后再引入FPGA的PCIe IPCORE复位端,即对PCIE_PERST_N信号做低脉冲时间计数,大于规定的ms级低电平才判断为复位,否则则判断为干扰信号,FPGA控制逻辑不去复位PCIE IPCORE。

3.第二个问题定位及解决过程

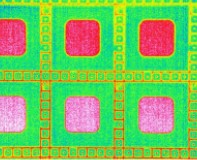

该问题的定位比第一个问题定位简单。因为该问题是在带电池低电量时必发,在插上交流电时则没有该现象,因此可以排除软件和FPGA逻辑问题,因此把问题聚焦在电源上。通过示波器实地测试,发现在电池低电量且工作于该模式下,电流有突然增大的现象,导致此时电压跌落,引发FPGA逻辑时钟失锁,由于FPGA逻辑的设计是使用逻辑系统时钟锁定信号作为PCIe IPCORE部分逻辑的复位信号,因此此时会导致FPGA的PCIe IPCORE被复位,进而产生PCIe通讯失效的现象。现在来分析一下整个过程,该时刻波形记录如下图所示: