图7WS2811/12数据格式

WS2811/12部件采用DIN(数据输入)和DOUT(数据输出)信号,以便简单地进行串行连接。每个部件都保留其看到的头24位数据,然后把剩余数据从DOUT引脚输出。参见下面的图8。

图8连接多个WS2811/12部件

当数据流启动后,每个部件将看到持续的数据流。如果数据信号的上升沿不超过50微秒,部件会锁存数据,将紧邻的24位数据视为自己的数据,并将其余数据重新发送出去。

图9数据流闲置时间超过50微秒时器件复位

正如您所看到的,其原理并不复杂,但它并不能轻松地适配到标准的微控制器硬件上。我确实发现有人使用SPI接口来维持时序,但这要求每个真实的数据位使用至少三个SPI数据位,对于通过位拆裂获得CPU性能而言优势不大。由于时序并不严格,如果您在固件中实现接口(位拆裂),CPU将专门用于翻转驱动信号直至LED全部更新。这意味着您需要禁用所有中断,在整个过程中不对任何其它输入做出响应。如果您有1,000个LED,则更新时间为(0.40微秒+0.85)*24位*1,000个LED=30,000微秒或30毫秒。这可能并不是什么问题,但如果您要以30Hz的频率更新LED,将几乎占用100%的CPU!在编写代码时,我习惯于在不得不较长时间禁用中断的地方避免阻塞代码或条件,特别在系统中有用户接口或是需要与其它处理器通信的情况下尤为如此。我的目的是尽量减轻CPU的负担,让硬件完成大部分工作,就如同今天常见的内部UART或SPI模块所做的工作一样。赛普拉斯PSoCUDB有几项特性能让这项工作变得非常简便。每个UDB在数据通路中有两个4字节FIFO和一个移位器。在实现UART时,您可将一个FIFO用作TX缓存,另一个用作RX缓存。对于WS2811/12,我只需要一个输出FIFO和移位器。我决定配置硬件,为每个器件每次生成一次中断。中断处理器将加载24位(3字节)数据,直到FIFO为空时返回。采用这种方法,可以每30微秒中断一次,而不必以150毫微秒或更短间隔禁用全部中断和位拆裂。我决定使用的微控制器是赛普拉斯PSoCCY8C4245AXI。该微控制器大批量采购价格约为一美元,有四个UDB,运行频率为48MHz,足以满足此项工作所需的速度和硬件要求。

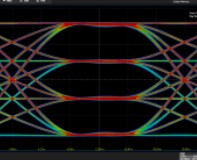

设计使用了PSoC提供的四个UDB中的两个。一个用于使用FIFO缓冲数据和移位数据,这样每个器件的全部24位(3字节)可一次性写入。第二个UDB可使用两个比较输出创建PWM。一个比较输出用于创建逻辑0,另一个用于创建逻辑1。该串行数据可用于控制数字多路复用器,选择波形1或0。敬请参见下图10的方框图。

图10WS2811/12接口使用PSoCUDB的方框图