图4. 一般电子战系统框图

硬件演示

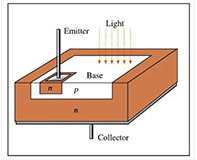

项目展示的是ADC接口和通道选择器功能。一个信号发生器产生一个正弦信号音,作为AD9625的输入。AD9625 ADC输出端通过行业标准FMC接口连接至Arria-V SoC开发套件。JESD204B标准定义了各种通道配置条件下逻辑器件的数据速率。在本演示中,JESD204B接口配置为使用8通道收发器模式,如图5A和图5B所示。

图5B. 面向Altera系统在环的通道选择器JESD204B输入和Avalon存储器图

通过JESD204B接口接收的样本馈入通道选择器IP中,后者配置为用16条输入线并行接收16个样本(图4中的参数M)。根据FFT点的数量,把一个全FFT帧分为多个时隙。例如,一个1024点FFT需要1024/16 = 64个时隙。滤波器组系数和FFT处理级会根据时隙自动切换。

通道选择器IP是用DSP高级版生成器(DSPBA)开发的,这是来自Altera的一款基于模型的设计流工具。借助该工具,信号处理工程师可以在MATLAB/Simulink环境中设计、评估和验证其算法。当算法为最优时,DSPBA会生成可以部署在Altera FPGA上的代码。

通道选择器输出存储在片内存储器中,并通过Altera系统在环(SIL)工具进行验证。SIL用一个MATLAB API来触发片内寄存器,开始记录,以用于数据可视化。一旦触发,则会对FFT处理执行一次迭代,并把产生的数据存储到片内SRAM中。MATLAB API通过Altera Avalon存储器图把数据从SRAM提取到MATLAB主机中。上传到MATLAB之后,则会在屏幕上绘制样本图。

IP的集成是在Qsys中完成的。Qsys是Altera推出的一款集成工具,通过提供集成框架,可以大幅缩短开发流程。运用图形用户界面即可实现层级式IP重用和互联基础设施。

创建一个Qsys项目,以集成通道选择器IP和JESD204B IP。除了通道选择器IP集成以外,项目还集成了控制功能,以支持连接ADC的SPI配置接口。

通道选择器可以通过MATLAB设置脚本轻松切换为不同的FFT大小。这种灵活性为将来的升级路径提供了保障,同时还有可能在不同系统配置之间实现设计的重复利用。例如,图6展示了来自SIL的4096点FFT输出。

图6. 4k-FFT通道选择器通过SIL的输出图示例

结论

通过新一代高速转换器打造的解决方案可以提供更高的瞬时带宽而不牺牲系统灵敏度,同时还能在频率规划方面提供更大的灵活性,或者消除前端RF带上的下混频级的必要性。然而,在1 GHz范围内实现带宽数据分析可能对高性能系统的设计造成挑战。

为了解决这个问题,可以利用通道选择器来分析这些宽带宽同时维持高性能。这些新型GSPS RF ADC加上新型可配置通道选择器IP内核为新一代系统设计师提供了一种更快的解决方案,可以很好地适应不断变化的电子战环境。