通道仿真

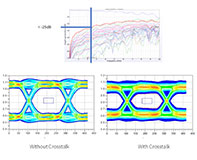

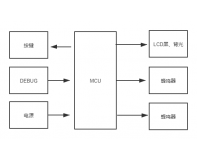

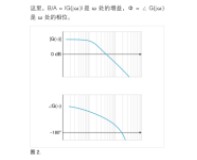

正如上文提到的,DDR5协议草案中,有低误码率的要求。如果使用传统的瞬态算法,就需要将5.3e9个bit逐一卷积计算,这将花费大量的时间,与仿真尽早,快速评估设计的初衷不符,也往往很难实现。 为此,在DDR5的仿真中,就必须使用类似于广泛应用于SERDES仿真当中的通道仿真技术。传统适用于SERDES的通道仿真分成两种模式,其一是逐bit模式(bit-by-bit),这种方式会得到单个bit的阶跃响应,在通过仿真器根据输入的bit序列,将对应的阶跃响应进行叠加。而另一种则是统计模式(statistical),即整个系统的响应,包括抖动,串扰,均衡等,都是基于单个bit的阶跃响应,根据概率密度分布结果,经过数据后处理获得。由于DDR信号多为单端信号,与SERDES的差分信号不同。因此,应用在DDR上的通道仿真技术,还需要有一些改动。首先是通道仿真技术所需要的阶跃响应。差分信号的上升沿与下降沿是对称的,因此只需要获得单一的阶跃响应进行通道仿真。而对于单端信号而言,上升时间和下降时间不再相同,这就意味着需要同时获得上升和下降两个阶跃响应,同时,仿真器需要在信号上升和下降时使用对应阶跃响应进行计算。

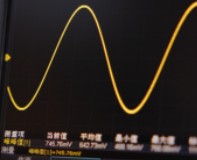

其次是时钟问题。SERDES信号往往是通过时钟恢复电路(CDR),从信号本身恢复出时钟信号。而DDR则不同,DQ信号由DQS信号触发。这就需要仿真器具有时钟触发的功能。否则,如果依旧使用DQ信号本身进行时钟恢复的话,会造成时域的偏移。下图中,红色部分为DQ时钟恢复后结果,蓝色为DQ由DQS触发后的结果。可以看到,两个结果在时间上存在一个偏移量。

最后是关于DDR的write-leveling功能。Write-leveling允许设备调整ClK信号与DQS信号之间的时间差。如果仿真器不能实现这个功能,会带来不必要的调整。

在这里需要注意的是,如果需要使用Rx端DFE的自适应模式,必须在bit-by-bit模式下进行仿真。而statistical模式下,只支持固定抽头系数的仿真。