在Memory Designer中,只需要一张原理图便可以分别进行通道和瞬态仿真。而由于总线形式的使用,则将传统设置方法所需的数小时,缩减至数分钟,同时也减小了设置错误的风险。

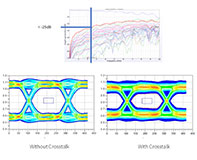

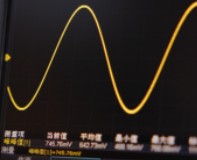

此外,Memory Designer中的DDR BUS仿真器,可以根据信号的上升与下降,使用对应的阶跃响应,获得正确的波形。如下图所示,DDR BUS仿真器在上升沿与下降沿不对称的情况下,有很高的精确度。

另一方面,基于Keysight成熟的通道仿真算法,DDR BUS仿真器可以根据AMI模型中的均衡算法,对信号进行均衡,同时可以准确预测在低误码率情况下的抖动对信号的影响。在下图中也可以发现,当DQ与DQS存在时间差时,会造成眼图的偏移。

05 ADS DDR5仿真实例

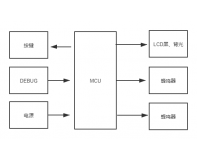

图中显示了在ADS Memory Designer环境中DDR5基本的仿真结构,所有信号以总线形式连接,设置过程只需要短短几分钟。其中控制器和内存模块都使用了IBIS-AMI模型,并且允许对AMI模型中的参数进行编辑。

图中显示了DDR5在ADS Memory Designer 中的仿真结果。可以发现,经过AMI模型中均衡算法处理的DQ信号,眼图张开程度明显增加。