其中VDD - VDS_high表示电源轨电压和高压端场效应晶体管FET上的压降。需要注意,在开启期间,由于VDD是固定的,而VDS_high是高压端场效应晶体管FET本体二极管上的电压,所以这个量是恒定的。

■ Rshunt是分流电阻

■ ID是根据Rshunt上的压降测得的漏极电流

■ dID/dt 是测得的漏极电流变化率

■ Leff是整个电源回路的有效电感

如上所述,在开启期间,VDD-VDS_high实际上是恒定的。Rshunt和Leff也是恒定的。这意味着模拟的VDS_low走线波形是ID的函数。

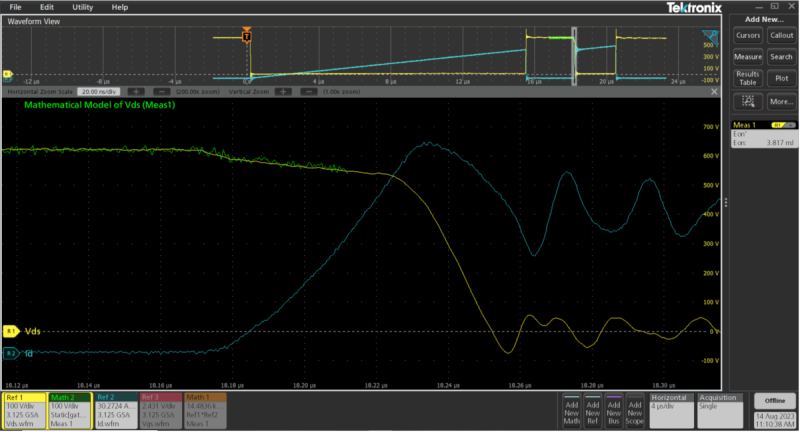

配置完参数后,用户按下WBG的deskew按钮。系统将根据指定的参数和漏极电流生成VDS的数学模型。该波形将显示在屏幕上。

图4. 根据ID计算出的VDS对齐波形与测量的VDS波形进行比较。偏移是对齐波形和测量波形之间的时间差。计算出偏斜后,就可以从ID波形中去除偏斜

如上图所示,有效电感Leff考虑到了整个环路的“叠加”。因此,Leff通常是未知的,而这个参数需要反复调整。简单地将纠偏过程反复运行,并对Leff进行调整,直到计算出的对齐波形和测量出的VDS波形具有相同的形状。如果计算出的VDS对齐波形与测量的VDS波形在形状上存在差异,可以调整参数并再次运行校准时间偏差。

一旦参数设置准确,对齐波形和测量波形将具有相同的形状,系统就能确定并纠正偏斜。偏斜值显示在Deskew设置中,并自动应用于连接VDS信号的通道。

这一新流程可以准确地计算偏斜值,并将时序偏差校准时间从一小时或更长时间缩短到5至10分钟。