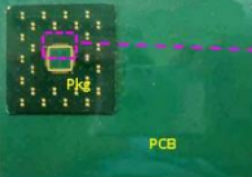

图5 去耦电容安装在Pkg和PCB上

如图5所示,我们摆放电容的位置分三种情况,一是在Pkg上加52颗,二是在PCB上加63颗,三是在Pkg和PCB上同时各放置52和63颗,电容值大小为100nF, ESR、ESL分别为0.04ohm、0.63nH。量测结果如图6。

图6 加去耦电容于不同位置的|S21|比较图

首先,把低频到5Ghz分成三个阶段,首先,开始低频到500Mhz左右,不管在Pkg或PCB上加去耦电容,相比没有加电容,都可以大大降低结构阻抗,减少GBN干扰。第二,对于0.5Ghz~2Ghz,在Pkg上和同时在Pkg与PCB上加去耦电容,对噪声抑制效果差不多。可是如果只在PCB上加电容,可以看到在800Mhz附近多了一个共振点,这比没有加电容时更糟。所以我们只在PCB上加电容时要特别注意,可能加上电容后电源噪声更严重。第三,从2Ghz~5Ghz,三种加电容方式与没加电容相比,效果并不明显,因为此阶段超过了电容本身的共振频率,由于电容ESL的影响,随着频率升高,耦合电容逐渐失去作用,对较高频的噪声失去抑制效果。

去耦电容ESR的影响

在Pkg结合PCB结构上,放置12颗去耦电容,同时改变去耦电容的ESR,模拟结果如图7所示。可以发现,当ESR值越来越大,会将极点铲平,同时零点也被填平,使S21成为较为平坦的曲线。

图7 去耦电容的ESR对|S21|的影响

去耦电容ESL的影响

在Pkg结合PCB结构上,放置12颗去耦电容,同时改变去耦电容的ESL,模拟结果如图8所示。从图中我们发现,ESL越大,共振点振幅越大,且有往低频移动的趋势,对噪声的抑制能力越低。

图8 去耦电容的ESL对|S21|的影响

去耦电容数量的影响

由前面的结果知道,电容放在封装上效果更好,所以对电容数量的探讨,以在Pkg上为主。在前述Pkg+PCB的结构上,Pkg上电容的放置方式如图9,模拟结果如图10。