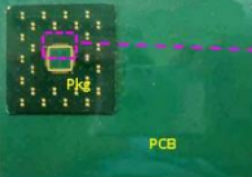

图12 不同Pkg电源层厚度对|S21|的影响

接着,我们固定Pkg厚度为0.15mm,分别改变PCB厚度为0.15mm、0.4mm、0.8mm、1.6mm,PCB厚度对S参数的影响结果如图13所示,可以看到PCB电源层厚度对整体趋势影响并不大,只有低频部分少有差异,厚度增加第一个零点小高频移动,高频部分只稍有差异。

图13 不同PCB电源层厚度对|S21|的影响

电容摆放距离的影响

我们知道去耦电容的位置距离噪声源越近越好,因为能减少电容到噪声源之间的电感值,让电容更快的吸收突波,降低噪声,达到稳定电压的作用。同样降低电源层厚度能减小电源平面寄生电感,也能起到相同作用。在模拟上我们改变电容在封装上和测试点之间的距离,分别为1.7cm和0.2cm,Pkg和PCB电源层厚度分两种情况,第一种Pkg 0.15mm和PCB 0.7mm,第二种情况,Pkg1.6mm和PCB 0.7mm,电容100nF、ESR 0.04ohm、ESL 0.63nH。

图15 不同电容与测试点的距离|S21|模拟结

由模拟结果得知,当因为封装结构或绕线问题,不能把电容放置在噪声源附近是,我们可以藉由减低Pkg电源层厚度,减少噪声的影响。

结论

最后,我们对高速数字电路如何抑制噪声做一总结。首先,去耦电容的理想位置是放置在Pkg上;ESR增大虽能把极点铲平,但也会导致共振频率深度变浅,电容充放电时间增大,会失去降低电源平面阻抗的功能;电容ESL增大会加快共振点后阻抗上升速度,所以ESL越低越好;电容数量越多越好,电容墙可以提高隔离效果;电容容值的选择,需要根据噪声频段来选择,尽量不要多容值混用,虽然这样能增加噪声抑制的频宽,但也会增加共振点数量,如果噪声刚好落在共振点上,叠加的效果可能会更严重;PCB电源平面厚度对Pkg上的S参数几乎没有影响,但在低频,Pkg上板层厚度却会影响PCB耦合上来的噪声大小,Pkg板层越薄耦合上来的噪声越小;高频部分,主要受封装影响,Pkg板层越薄,|S21|值越小。