设计中直接调用Altera公司提供的DDR2 SDRAM控制器,并选用一块它可以驱动的芯片来提高工作效率。芯片可使用的缓存空间是要重点关注的。每个通道都要分配固定的缓存区域,所以要将有限的内存空间作合理的划分。如果是图像数据,单个通道至少要有缓存两帧以上的空间。DDR2读写控制模块直接调用DDR2 SDRAM控制器IP核,但由于该IP核提供给用户端的接口使用不方便,需要按照其文档上介绍的时序来进行突发式读写。

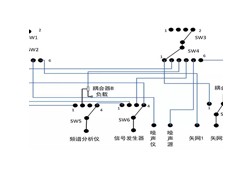

本模块的功能主要是协调各通道采集数据的写入和读出。如图3所示,写操作时,各通道的数据首先用FPGA资源进行缓存,然后写入控制状态机通过轮询的方式依次检查各个通道已经缓存的数据量,如果足够一次突发写,则将其写入SDRAM芯片的相应通道块中,然后再检查下一通道;读操作时,读出控制状态机也依次检查各个通道写入SDRAM芯片的数据量,如果足够一次突发读,则将其读出,通过网络发送出去。

基于以上控制方式,设计对各通道的数据格式是不作限制,如图1中所示,可以是PAL、Camera link、VGA等各种格式的图像或组合,只是在采集之前向上位机报告各个通道的数据信息。但需要说明的是,这些数据的带宽总和理论上不应超过千兆以太网的最大传输速率,这是采用轮询方式得以成功的前提。其实,如今普通PC机的处理能力远远不能达到这个最大限制,当速度到达100 Mbit·s-1时,上位机丢包就已经很严重。如果是将采集的数据在上位机上显示,最多可能只有70~80 Mbit·s-1;如果还要将数据写入硬盘,那数据率则会更低,除了配备一块上好的硬盘之外,还需要在上位机软件的优化上多作努力。