随着测试成本的继续降低,裸片上测试能力资源的广泛开发和应用不断向前推进。为了检验相关定时间题,日益采用传输故障的全速度结构测试、关键通路的通路延迟测试和BIST/环回技术。

结构全速度方法的一个例子是AC扫描,而EDA工具中对AC扫描的支持不断改进。然而,AC扫描测试期间的开关动作与功能测试是完全不同的,正是由于此原因,这不可以模拟真实的应用条件。因此,这样的方法需要的实际功能测试的广延相关性。甚至有良好的相关性,仍然会有其他可能的问题,导致成品率损失增加或测试漏失。

不精确的延迟测试可能是成品率损失和测试漏失的另一个原因。只有几十皮秒的延迟通路测量误差相当于内部时钟周期的5%。至今不知道对延迟通路测量加容限测试的方法,所以,这些误差可导致成品率损失或测试漏失。

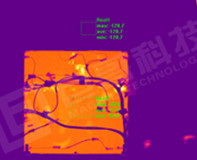

把片上BIST结构与串行环回方法相结合是全速度产品测试的另一种流行技术,特别是对于SerDes I/O单元的测试。用专门的ATE环回卡(如Agilent93000 BIST Assist6.4)可增强测试范围,除基本功能测试外也支持参量测量(图2)。

图2 BIST环回测试方法与专用ATE环回卡结合

尽管DFT或其他低成本技术对于高速器件的很多高频I/O特性是最经济的测试方案,但仍然对ATE有较强的要求,希望它能提供全速度激励和捕获,特别是在产品定型前更是这样。当DFT完全取代全速度功能测试时,可达到的故障覆盖率趋于折衷。这可能是一种潜在的风险,特别是对于把工艺技术推至极限的新I/O技术而言。

另外,DFT仍然是一种成熟的技术,而不同的硅供应商遵循不同的DFT开发战略。基于此原因,全速度DFT不是一贯的跨业界实现。甚至在生产中,在可预测的将来,整个业界将不希望用全速度DFT完全替代全速度功能测试。

高速ATE通道的关键要求